# TECHNICAL DATA

AN EXCLUSIVE RADIO SHACK SERVICE TO THE EXPERIMENTER

## SP0256-AL2 Voice Synthesizer

### Features

- Natural Speech

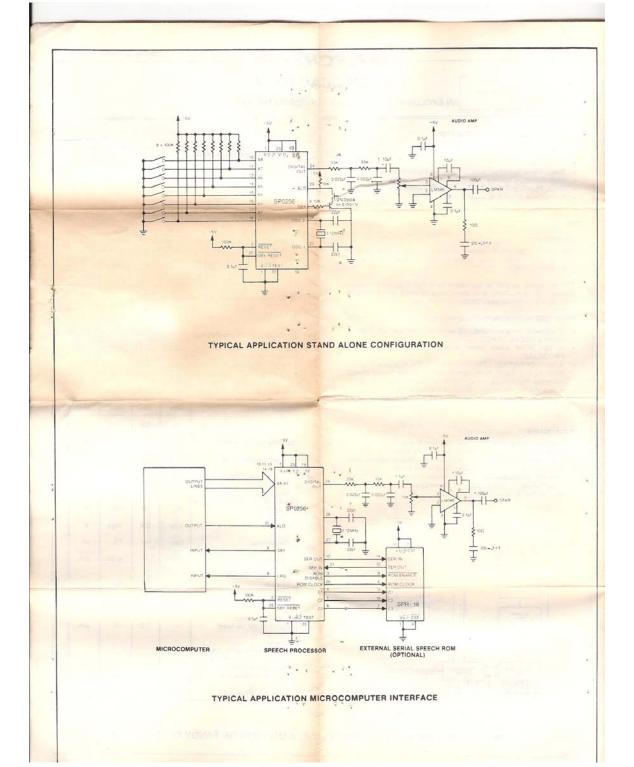

- Stand Alone Operation with Inexpensive Support Components

- Wide Operating Voltage

Word, Phrase, or Sentence Library, ROM Expandable

Expandable to 491K of ROM Directly

- Simple Interface to Most Microcomputers or Microprocessors Supports L.P.C. Synthesis: Formant Synthesis: Allophone

- Synthesis

#### Description

The SP0256 (Speech Processor) is a single chip N-Channel MOS LSI device that is able, using its stored program, to synthesize speech or complex sounds.

The achievable output is equivalent to a flat frequency response ranging from 0 to 5kHz, a dynamic range of 42dB, and a signal-to-noise ratio of approximately 35dB.

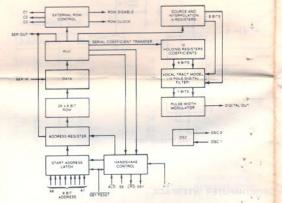

The SP0256 incorporates four basic functions:

- A software programmable digital filter that can be made to model a VOCAL TRACT.

A 16K ROM which stores both data and instructions (THE PROGRAM).

- A MICROCONTROLLER which controls the data flow from the A MICHOCONTROLLER which controls the data how from the ROM to the digital filter, the assembly of the "word strings" necessary for linking speech elements together, and the amplitude and pitch information to excite the digital filter.

A PULSE WIDTH MODULATOR that creates a digital output which is converted to an analog signal when filtered by an external low pass filter.

### Applications

- Telecommunications

- Appliances

- Computer Peripherals

Automotive

- Personal Computers

- Toys/Games

- Educational Aids

- Warning Systems

- Security Systems

Electronic Musical Instruments

- Aids to the Blind Narrow Bandwidth

- Communication Systems

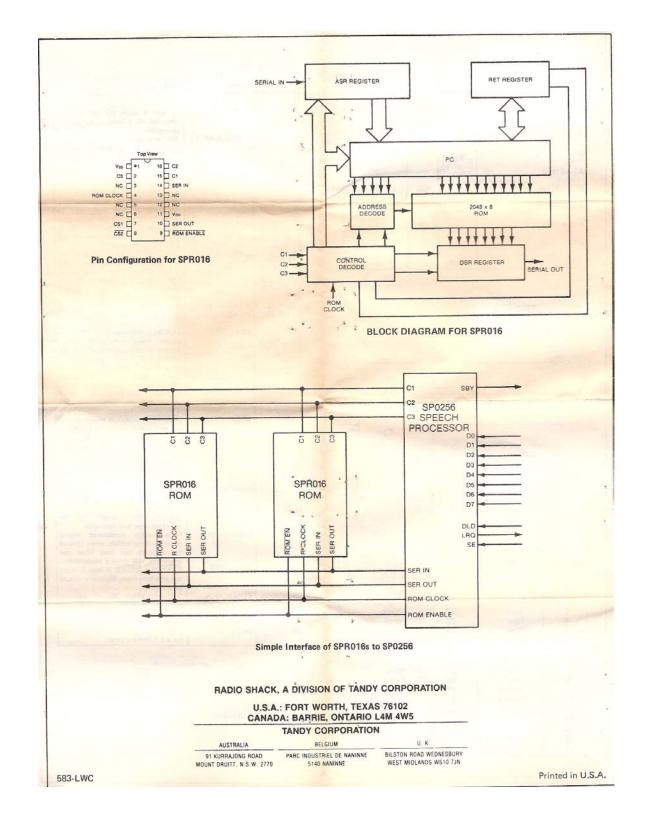

**BLOCK DIAGRAM FOR SPO256**

PIN CONFIGURATION V<sub>SS</sub> C •1 RESET C 2 DISABLE C 3 C1 C 4 C2 C 5

## Absolute Maximum Ratings

| V <sub>D1</sub> V <sub>DD</sub> |    |  |  |  |  |   |  |  | 0.3V to +12V   |

|---------------------------------|----|--|--|--|--|---|--|--|----------------|

| Storage Temperature             |    |  |  |  |  | * |  |  | 25°C to +125°C |

| Clock Crystal Frequenc          | y. |  |  |  |  |   |  |  | 3.12MHz        |

DC CHARACTERISTICS

Operating Temperature TA = 0°C to +70°C

|     | Characteristics                                                                                  | Sym              | Min | Max             | Units |

|-----|--------------------------------------------------------------------------------------------------|------------------|-----|-----------------|-------|

|     | Primary Supply Voltage                                                                           | VDD              | 4,6 | 7               | ٧     |

|     | Standby Supply Voltage                                                                           | V <sub>D1</sub>  | 4,6 | 7               | V     |

|     | Primary Supply Current                                                                           | 1DD              | _   | 90              | mA    |

|     | Standby Supply Current                                                                           | I <sub>D1</sub>  | -   |                 | mA    |

|     | Inputs<br>A1-A8, ALD, SER IN, TEST, St<br>Logic 0                                                | E VIL            | 0   | 0.6             | v     |

|     | Logic 1                                                                                          | VIH              | 2.4 | V <sub>D1</sub> | ٧     |

| 4 2 | Capacitance                                                                                      | CIN              | _   | 10              | pf    |

|     | Leakage                                                                                          | ILC              | -   | <u>+</u> 10     | μΑ    |

|     | RESET, SBY RESET                                                                                 | VIL1             | 0   | 0,6             | V     |

|     | Logic 1                                                                                          | V <sub>IH1</sub> | 3.6 | V <sub>D1</sub> | V     |

|     | Oscillator Leakage<br>OSC 1 (7.0V, no load)                                                      | -                | 1.0 | 10              | μА    |

|     | Outputs SBY, DIGITAL OUT, C1, C2, C3, LRQ, ROM DISABLE, ROM CLOCK, SER OUT Logic 0 (0.72mA load) | VOL              | 0   | 0.6             | V     |

|     | Logic 1 (-50µA load)                                                                             | Voн              | 3.5 | V <sub>D1</sub> | ٧     |

CUSTOM PACKAGED IN USA BY RADIO SHACK, A DIVISION OF TANDY CORPORATION

AC CHARACTERISTICS

Operating Temperature: T<sub>A</sub> = 0°C to +70°C

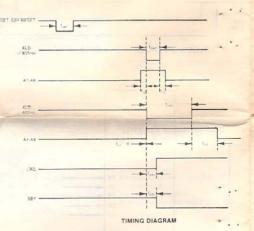

| Characteristics            | Sym              | Min  | Max | Units  |

|----------------------------|------------------|------|-----|--------|

| Clock Frequency, 3.120 MHz | -                | -    | -   | MHz    |

| Reset, SBY Reset           | tpw1             | 100  | -   | μs - ' |

| ALD (<800ns)               | tpw2             | 200  | 800 | ns     |

| A1-A8 Set Up               | t <sub>\$2</sub> | 160  | -   | ns     |

| A1-A8 Hold                 | th2              | 160  | -   | ns     |

| ALD (≥800ns)               | tpw3             | 800  | = 1 | ns     |

| A1-A8 Set Up               | t <sub>s</sub> 3 | 0    | -   | ns     |

| A1-A8 Hold                 | th3              | 1200 | -   | ns     |

| LRQ .                      | tpd0             | -    | 640 | ns     |

| SBY                        | tpd0             | 7    | 640 | ns 3   |

# Vocabulary List

| Address | Word      | Address | Word             |

|---------|-----------|---------|------------------|

| 0       | Oh        | 18      | Eighteen -       |

| 1       | One       | 19      | Nineteen         |

| 2       | Two       | 20      | Twenty           |

| 3       | Three     | 21      | Thirty           |

| 4 5     | Four      | 22      | Forty            |

| 5       | Five      | 23      | Fifty            |

| 6       | Six       | 24      | It Is            |

| 7       | Seven     | 25      | A.M.             |

| 8       | Eight     | 26      | P.M.             |

| 9       | Nine      | 27      | Hour             |

| 10      | Ten       | 28      | Minute .         |

| 11      | Eleven    | 29      | Hundred Hour     |

| 12      | Twelve    | 30      | Good Morning     |

| 13      | Thirteen  | 31      | Attention Please |

| 14      | Fourteen  | 32      | Please Hurry .   |

| 15      | Fifteen   | 33      | Melody A         |

| 16      | Sixteen   | 34      | Melody B         |

| 17      | Seventeen | 35      | Melody C         |

# PIN FUNCTIONS

| Pin Number | Name            | Function                                                   |

|------------|-----------------|------------------------------------------------------------|

| 1          | V <sub>SS</sub> | Ground                                                     |

| 2          | RESET           | A logic O resets the SP. Must I                            |

|            | 110001          | returned to a logic 1 for norm                             |

|            |                 |                                                            |

|            |                 | operation.                                                 |

| 3          | ROM DISABLE     | For use with an external seri                              |

|            |                 | speech ROM, A logic 1 disabl                               |

|            |                 | the external ROM.                                          |

| 4,5,6      | C1,C2,C3        | Output control lines used by a                             |

| 1,0,0      | 01,02,00        | external serial speech ROM,                                |

|            |                 |                                                            |

| 7          | VDD             | Primary power supply.                                      |

| 3          | SBY             | STANDBY. A logic 1 output inc                              |

|            |                 | cates that the SP is inactive (i. not talking) and VDD can |

|            |                 | not talking) and Von can I                                 |

|            |                 | not tarking and vob car i                                  |

|            |                 | powered down externally to co                              |

|            |                 | serve power. When the SP is reac                           |

|            |                 | vated by an address being loade                            |

|            |                 | SBY will go to logic 0.                                    |

|            | TRO             | LOAD REQUEST. LRQ is a log                                 |

|            |                 | 1 autout whosever the least buff                           |

|            |                 | 1 output whenever the input buff                           |

|            |                 | is full. When LRQ goes to a logic                          |

|            |                 | the input port is loaded by placing                        |

|            |                 | the 8 address bits on A1-A8 ar                             |

| 5          |                 | pulsing the ALD input.                                     |

| 0 11 10    | 40 47 46 AE     | 8-bit address which defines any or                         |

| 10,11,13,  | A8,A7,A6,A5,    |                                                            |

| 14,15,16,  | A4,A3,A2,A1     | of 256 speech entry point                                  |

| 17,18      |                 | The second state of the second                             |

| 12         | SER OUT         | SERIAL ADDRESS OUT. Th                                     |

|            |                 | output transfers a 16-bit addre                            |

|            |                 |                                                            |

| 100        |                 | serially to an external speech ROM                         |

| 19         | SE              | STROBE ENABLE. Normally he                                 |

|            |                 | in a logic 1 state. When tied t                            |

|            |                 | ground, ALD is disabled and th                             |

| -          |                 | SP will automatically latch in th                          |

|            |                 | address on the input bus approx                            |

|            |                 |                                                            |

|            |                 | mately 1 us after detecting a log                          |

| les:       |                 | 1 on any address line.                                     |

| 20         | ALD             | ADDRESS LOAD, A negative puls                              |

|            |                 | on this input loads the 8 addre                            |

|            |                 | bits into the input port. Th                               |

|            |                 | leading edge of this pulse cause                           |

|            |                 |                                                            |

|            |                 | LRQ to go high.                                            |

| 21         | SER IN          | SERIAL IN. This is an 8-bit seri                           |

|            |                 | data input from an external speed                          |

| 4          |                 | ROM.                                                       |

| 10         | TEST            | A logic 1 places the SP in te                              |

| 22         | 1631            | A logic I places the SP III te                             |

|            |                 | mode. This pin should normall                              |

|            |                 | be grounded.                                               |

| 3          | V <sub>D1</sub> | Standby power supply for th                                |

|            |                 | interface logic and controller.                            |

| 24         | DIGITAL OUT     | Pulse width modulated digital                              |

| 4          | DIGITALOUT      |                                                            |

|            |                 | speech output which, when filtere                          |

| 112        |                 | by a 5kHz low pass filter an                               |

|            |                 | amplified, will drive a loudspeake                         |

| 5          | SBY RESET       | STANDBY RESET, A logic 0 reser                             |

|            |                 | the interface logic. Normally shoul                        |

|            |                 |                                                            |

|            |                 | be a logic 1.                                              |

| 16         | ROM CLOCK       | 1.56MHz clock for an externa                               |

|            |                 | serial speech ROM.                                         |

| 7          | OSC 1           | XTAL IN. Input connection for                              |

|            |                 | 3.12MHz crystal.                                           |

|            | 0000            | XTAL OUT, Output connection                                |

|            | OSC 2           | AIAL OUI, Output connection                                |

| 8          |                 | for a 3.12MHz crystal.                                     |